# DRAM World-line Bottom Roughness Detection Using BSE Signal

line 1: 1st Linghai Liu line 2: Changxin Memory Techonologies,Inc.

line 3: <u>Linghai.Liu@cxmt.com</u>

line 1: 4th Al Zhang line 2: Changxin Memory Techonologies,Inc. line 3: Al.Zhang@cxmt.com

line 1: 2nd Laura Luo line 2: Changxin Memory Techonologies,Inc.

line 3: <u>Laura.Luo@cxmt.com</u>

line 1: 5th Musa Zhuang line 2: Changxin Memory Techonologies,Inc.

line 3: Musa.Zhuang@cxmt.com

line 1: 3rd Peter Park line 2: Changxin Memory Techonologies,Inc. line 3: Peter.Park@cxmt.com

line 1: 6th Jerome Hu line 2: Changxin Memory Techonologies,Inc. line 3: Jerome.Hu@cxmt.com line 1: 7th Vincent Wu line 2: Changxin Memory Techonologies,Inc.

line 3: Vincent.Wu@cxmt.com

line 1: 8th Xiang Zhang line 3: Changxin Memory Techonologies,Inc. line 3: Xiang3.Zhang@cxmt.com

#### I. INTRODUCTION

In DRAM fabrication process, scanning electron microscope provides critical dimension and roughness measurement. However, during BWL process inline control, traditional topography CD and roughness measurement using SE images can not completely meet requirements of process control. The BWL is a deep trench, not only the top position but also bottom position measurement is necessary. So BSE is introduced to detect deeper bottom position CD and roughness. BSE images also have good material distinction to help detect bottom position signal. Fig. 1 shows the top view and cross-section of BWL. In general, the top position is detected and measured in traditional CDSEM measurement but the trench bottom position is an important part which we want to detect.

Fig. 1. BWL top view(left) and cross-section(right)

In BSE mode, the working point offers more energy and electrons to collect more BSE signal for deeper detection. The LER/LWR/Wiggling and CD value can be measured when BSE signal emits from the BWL trench bottom using CDSEM.

#### II. METHODOLOGY

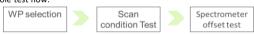

A new approach of BWL bottom profile detection and measurement is demonstrated in this paper. Different working point setting and parameters were applied to obtain SEM images. The 800V-70 pA working point (beam energy: 800V; I probe: 70pA) was used to detect the BWL bottom. The bottom edge can be seen but not clearly enough on account of some noise. So different scan parameters were tested to get better image quality. Pixel size and measurement box size were fixed. Scan rate with 1TV, slow1, slow2, slow3 and frame with 1 to 8 were tested. Reducing the scan rate or increasing the scan frames improves the image quality but impacts the throughput. Therefore, slow2 scan rate and 8 frames were chosen for balance. In BSE mode, spectrometer offset sets the energy filter (EF) value of the working point, which impacts resolution and signal intensity. The bigger absolute value EF, the better resolution but weaker signal intensity. As a result, different EF values test is needed. According to the above tests, the BWL trench bottom position CD, LER, LWR and Wiggling were measured with the best condition within this study. Fig.2 shows the whole test flow:

Fig. 2. Image Grab setting test flow

III. EXPERIMENT

Measurement on One Product Wafer at Different Process Steps

The same approach was used to detect BWL bottom information at two different process steps. As shown in Fig.7, in BWL process flow, the bottom trench surface of step1 is silicon (Si), and in step2 the BWL will be filled partially with titanium nitride (TiN).

Fig. 7. BWL of different process steps are observed

1) BWL CD and roughness measurement on wafer at step1: The CD SEM recipe was created, which CD and roughness were measured on product wafer with full map. For the bottom position feature measurement, BSE detection was utilized. And for top position feature, traditional SE image was applied. Measurement images are shown in Fig.8.

Fig. 8. BWL surface with Si measurement image at step1

2) BWL CD and roughness measurement on wafer at step2: When the wafer arrived at process step2, BWL surface was filled with TiN partially, the same wafer bottom position is measured as below in Fig.9.

Fig. 9. BWL surface with Si measurement image at step2

CD and Roughness Results at Different Process Steps on One Wafer

For full map BWL CD value, the mean value of process step2 bottom position CD is ~2 nm larger than the mean value of step1 bottom position CD. BWL is an inverted-trapezoidal trench with bigger top and smaller bottom due to the limitation of etch process, hence it is reasonable that the bottom CD of step2 is bigger than step1 as the bottom position of step2 is higher than previous step in the vertical direction. Site by site chart of CD value is illustrated as Fig.10.

Fig. 10. Chart of site by site bottom CD value and mean value at step1 and step2

As CD pitch goes down, device performance is impacted by line/space roughness much more seriously. So roughness items (LER, LWR and Wiggling) were also measured. Line edge roughness (LER) represents the meandering of a single line edge while line width roughness (LWR) reveals the variation of CD value along line/space length. And Wiggling may affect OVL and cause edge position errors.

Fig.11 and Fig.12 show BWL bottom position LER and LWR site by site chart at different process steps, respectively. Both LER left and right increased from step1 to step2, which indicates the bottom morphology of BWL deteriorates at step2.

Fig. 11. Chart of site by site bottom LER left and right value and mean value at step1 and step2

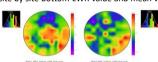

In Fig.12, LWR seemed to be reduced from step1 to step2, but it is noted that the 3 sigma of LWR at step2 (3 sigma=1.4) is much larger than step1(3 sigma=0.3) as illustrated in Fig.13, which reveals the variation of CD value worsened at step2.

Fig. 12. Chart of site by site bottom LWR value and mean value at step1 and step2

Fig. 13. Heat map of bottom LWR value at step1 and step2

Wiggling measurement is applied in this work and the Wiggling calculation is as below formula in this CDSEM machine:

$$Wiggling\_L = \alpha \frac{LER_{LF}}{LWR}$$

(1)

Fig.14 describes that the Wiggling of step2 is far larger than step1, which strongly confirms the roughness becomes much worse at step2.

Fig. 14. Chart of site by site bottom Wiggling value and mean value at step1 and step2

## IV. CONCLUTION

In this work we present: Demonstration of the approach of BWL bottom roughness detection by using BSE signal. Optimizing scan and detection parameters obtained better resolution the BWL bottom roughness is measured successfully by utilizing BSE mode. According to the analysis of CD, LER, LWR and Wiggling value and 3 sigma of 2 process steps, we found BWL roughness turns worse from step1 to step2 as LER (both left and right) and Wiggling value increases significantly at step2. LWR value is a little larger at step1 but its 3 sigma is much smaller than step2, which indicates the roughness became terrible at step2 as well. All roughness items studied within this work reveal that the bottom surface topography of BWL turns worse at step2.

Compared the bottom position CD value, LER, LWR and Wiggling in different process steps, we found the key process that needed to be improved. By this way, we can detect more information about the BWL space roughness and set up a new way for CDSEM measurement and process inline monitoring.

## REFERENCES

[1] X. Zhang, M. Karakoy, K. Wu, Z. Chen, Z. Ge and N. Krishnan, "Inline detection for FinFET gate poly footing using e-Tilt metrology" 2018 29th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC), 2018, pp. 320-323.

[2] T. Schloesser, F. Jakubowski, J. v. Kluge, A. Graham, S. Slesazeck and M. Popp, "6F2 buried wordline DRAM cell for 40nm and beyond" 2008 IEEE International Electron Devices Meeting, 2008, pp. 1-4.

[3] I.-G. Kim, S.-H. Park, J.-S. Yoon, D.-J. Kim, J.-Y. Noh and J.-H. Lee, "Overcoming DRAM scaling limitations by employing straight recessed channel array transistors with <100> uniaxial and [100] uni-plane channels" IEEE International Electron Devices Meeting, 2005. IEDM Technical Digest., 2005, pp. 319-322.

[4] Z. Zou and S. K. Lim, "Image based CD SEM tool Real Time Monitoring," 2021 32nd Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC), 2021, pp. 1-4.

[5] Y. Ose, M. Ezumi and H. Todokoro, "High resolution CD-SEM system," Proceedings Eighth Asian Test Symposium (ATS'99), 1999, pp. 383-388.

## ACKNOWLEDGMENT

The authors would like to thank my team members who were contribute a lot about experiments